The assignment is the basic mechanism for placing values into nets and variables. There are two basic forms of assignments:

— The continuous assignment, which assigns values to nets

— The procedural assignment, which assigns values to variables

There are two additional forms of assignments, assign/de-assign and force/release, which are called procedural continuous assignments.

An assignment consists of two parts, a left-hand side and a right-hand side, separated by the equals ( = )

character; or, in the case of nonblocking procedural assignment, the less-than-equals ( <= ) character pair.

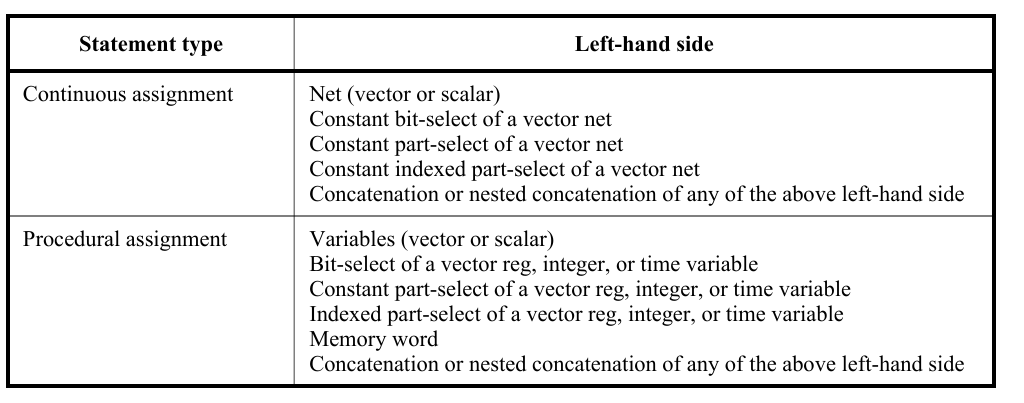

The right-hand side can be any expression that evaluates to a value. The left-hand side indicates the variable to which the right-hand side value is to be assigned. The left-hand side can take one of the forms given in below Table, depending on whether the assignment is a continuous assignment or a procedural assignment.