All four equality operators shall have the same precedence.

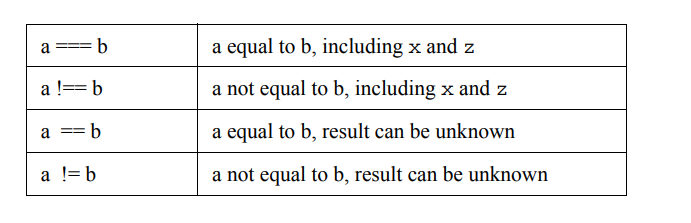

For the logical equality and logical inequality operators (== and !=), if, due to unknown or high-impedance bits in the operands, the relation is ambiguous, then the result shall be a 1-bit unknown value (x).

For the case equality and case inequality operators (=== and !==), the comparison shall be done just as it is in the procedural case statement (see 9.5). Bits that are x or z shall be included in the comparison and shall match for the result to be considered equal. The result of these operators shall always be a known value, either 1 or 0.