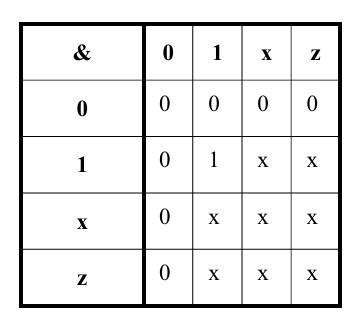

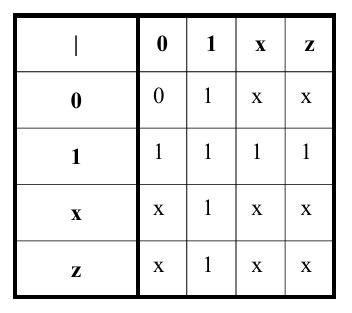

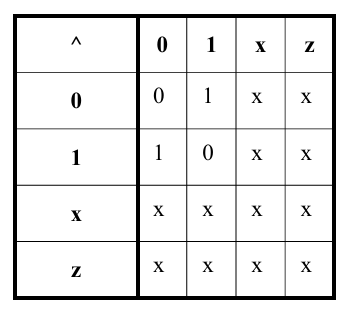

The unary reduction operators shall perform a bitwise operation on a single operand to produce a single-bit result. For reduction and, reduction or, and reduction xor operators, the first step of the operation shall apply the operator between the first bit of the operand and the second using below logic Tables.

The second and subsequent steps shall apply the operator between the 1-bit result of the prior step and the next bit of the operand using the same logic table.

Reduction unary and operator:

Reduction unary or operator:

Reduction unary exclusive or operator:

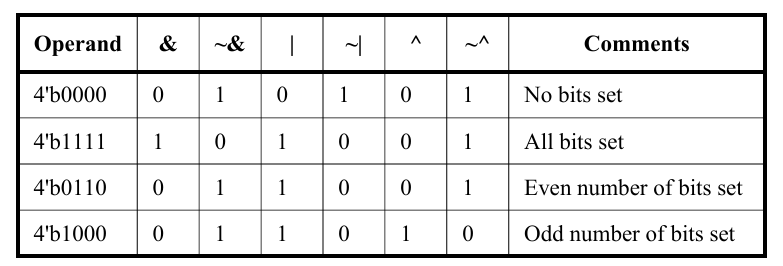

For example: below table shows the results of applying reduction operators on different operands-