Mainly Data types are used to represent the data storage and transmission elements in digital hardware.

Lets understand all fundamentals about Data types-

Value set:

It have four basic values-

0 – represents a logic zero, or a false condition

1 – represents a logic one, or a true condition

x – represents an unknown logic value

z – represents a high-impedance state

Here – X i.e unknown value might be either 0 or 1.

Nets and variables:

There are two main groups of data types: the variable data types and the net data types. These two groups differ in the way that they are assigned and hold values.

Net types: Net can represent physical connections between structural entities, such as gates. A net shall not store a value (except for the trireg net).

If no driver is connected to a net, its value shall be high-impedance (z) unless the net is a trireg, in which case it shall hold the previously driven value.

There are several distinct types of nets-

Wire and tri nets:

The wire and tri nets connect elements. The net types wire and tri shall be identical in their syntax and functions; two names are provided so that the name of a net can indicate the purpose of the net in that model. A wire net can be used for nets that are driven by a single gate or continuous assignment. The tri net type can be used where multiple drivers drive a net.

A variable: shall store a value from one assignment to the next. The default initialization value for reg, time, and integer data types shall be the unknown value, x.

Vectors: A net or reg declaration without a range specification shall be considered 1 bit wide and is known as a scalar. Multibit net and reg data types shall be declared by specifying a range, which is known as a vector.

Vector nets and regs shall obey laws of arithmetic modulo-2 to the power n (2n), where n is the number of bits in the vector. Vector nets and regs shall be treated as unsigned quantities, unless the net or reg is

declared to be signed or is connected to a port that is declared to be signed.

For example:

wand w; // a scalar net of type "wand"

tri [15:0] busa; // a three-state 16-bit bus

trireg (small) storeit; // a charge storage node of strength small

reg a; //scalar reg

reg[3:0] v; // a 4-bit vector reg made up of (from most to least significant)v[3], v[2], v[1], and v[0]

reg signed [3:0] signed_reg; // a 4-bit vector in range -8 to 7

reg [-1:4] b; // a 6-bit vector reg

wire w1, w2; // declares two wires

reg [4:0] x, y, z; // declares three 5-bit regs

Regs:

Assignments to a reg are made by procedural assignments. Because the reg holds a value between assignments, it can be used to model hardware registers. Edge-sensitive (i.e., flip-flops) and level sensitive (i.e., reset-set and transparent latches) storage elements can be modeled.

For example:

reg a; // a scalar reg

reg[1:0] v; // a 2-bit vector reg made up of v[1], and v[0]

wire w1, w2; // declares two wires

Integers, reals, times, and realtimes:

An integer is a general-purpose variable used for manipulating quantities that are not regarded as hardware registers.

A time variable is used for storing and manipulating simulation time quantities in situations where timing checks are required and for diagnostics and debugging purposes. This data type is typically used in conjunction with the $time system function.

For example:

integer a; // integer value

time last_chng; // time value

real float ; // a variable to store a real value

realtime rtime ; // a variable to store time as a real value

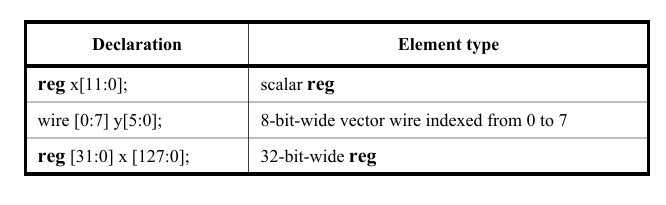

Arrays:

Arrays can be used to group elements of the declared element type into multidimensional objects. Arrays shall be declared by specifying the element address range(s) after the declared identifier.

Memory:

A one-dimensional array with elements of type reg is also called a memory. These memories can be used to model read-only memories (ROMs), random access memories (RAMs), and reg files. Each reg in the array is known as an element or word and is addressed by a single array index.

Array declarations examples:

reg [7:0] mema[0:255]; // declares a memory mema of 256 8-bit // registers. The indices are 0 to 255

integer inta[1:64]; // an array of 64 integer values

Assignment to above array elements-

mema = 0; // Illegal syntax- Attempt to write to entire array

arrayb[1] = 0; // Illegal Syntax - Attempt to write to elements // [1][0]..[1][255]

arrayb[1][12:31] = 0; // Illegal Syntax - Attempt to write to // elements [1][12]..[1][31]

mema[1] = 0; // Assigns 0 to the second element of mema

arrayb[1][0] = 0; // Assigns 0 to the bit referenced by indices // [1][0]

inta[4] = 33559; // Assign decimal number to integer in array

chng_hist[t_index] = $time; // Assign current simulation time to element addressed by integer index

Parameters:

Parameters do not belong to either the variable or the net group. Parameters are not variables; they are constants. There are two types of parameters: module parameters and specify parameters. It is illegal to redeclare a name already declared by a net, parameter, or variable declaration.

Both types of parameters accept a range specification. By default, parameters and specify params shall be as wide as necessary to contain the value of the constant, except when a range specification is present.

For example:

parameter msb = 7; // defines msb as a constant value 7

parameter e = 25, f = 9; // defines two constant numbers

parameter r = 5.7; // declares r as a real parameter

parameter byte_size = 8, byte_mask = byte_size - 1;

parameter average_delay = (r + f) / 2;

parameter signed [3:0] mux_selector = 0;

Parameters represent constants; hence, it is illegal to modify their value at run time. However, module parameters can be modified at compilation time to have values that are different from those specified in the declaration assignment. This allows customization of module instances. A parameter can be modified with the defparam statement or in the module instance statement. Typical uses of parameters are to specify delays and width of variables.

<< Previous | Next >>