The Verilog HDL has two types of explicit timing control over when procedural statements can occur. The

first type is a delay control, in which an expression specifies the time duration between initially encountering the statement and when the statement actually executes. The delay expression can be a

dynamic function of the state of the circuit, but it can be a simple number that separates statement executions in time. The delay control is an important feature when specifying stimulus waveform descriptions.

The second type of timing control is the event expression, which allows statement execution to be delayed until the occurrence of some simulation event occurring in a procedure executing concurrently with this procedure. A simulation event can be a change of value on a net or variable (an implicit event) or the occurrence of an explicitly named event that is triggered from other procedures (an explicit event). Most often, an event control is a positive or negative edge on a clock signal.

The procedural statements encountered so far all execute without advancing simulation time. Simulation

time can advance by one of the following three methods:

— A delay control, which is introduced by the symbol #

— An event control, which is introduced by the symbol @

— The wait statement, which operates like a combination of the event control and the while loop

1). Delay control:

A procedural statement following the delay control shall be delayed in its execution with respect to the

procedural statement preceding the delay control by the specified delay. If the delay expression evaluates to an unknown or high-impedance value, it shall be interpreted as zero delay. If the delay expression evaluates to a negative value, it shall be interpreted as a twos-complement unsigned integer of the same size as a time variable. Specify parameters are permitted in the delay expression. They can be overridden by SDF annotation, in which case the expression is reevaluated.

For example —The next three examples provide an expression following the number sign (#). Execution of the assignment is delayed by the amount of simulation time specified by the value of the expression.

#d rega = regb; // d is defined as a parameter

#((d+e)/2) rega = regb; // delay is average of d and e

#regr regr = regr + 1; // delay is the value in regr

2). Event control:

The execution of a procedural statement can be synchronized with a value change on a net or variable or the occurrence of a declared event. The value changes on nets and variable can be used as events to trigger the execution of a statement. This is known as detecting an implicit event. The event can also be based on the direction of the change, that is, toward the value 1 (posedge) or toward the value 0 (negedge).

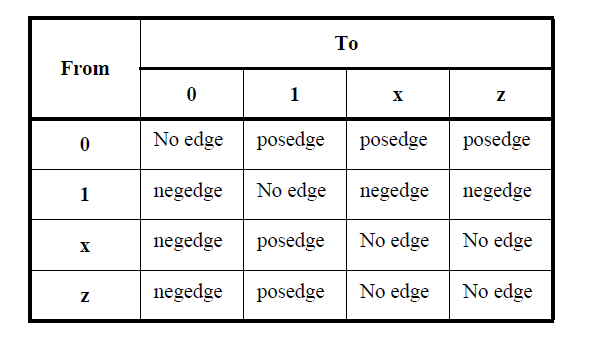

— A negedge shall be detected on the transition from 1 to x, z, or 0, and from x or z to 0

— A posedge shall be detected on the transition from 0 to x, z, or 1, and from x or z to 1

Below table shows detecting posedge & negedge-

The following example shows illustrations of edge-controlled statements:

@r rega = regb; // controlled by any value change in the reg r

@(posedge clock) rega = regb; // controlled by posedge on clock

@(negedge clock) rega = regb; // controlled by negative edge

3). Named events:

A new data type, in addition to nets and variables, called event can be declared. An identifier declared as an event data type is called a named event. A named event can be triggered explicitly. It can be used in an event expression to control the execution of procedural statements in the same manner as event controls.

An event shall not hold any data. The following are the characteristics of a named event:

— It can be made to occur at any particular time.

— It has no time duration.

— Its occurrence can be recognized by using the event control

An event-controlled statement (for example, @trig rega = regb;) shall cause simulation of its

containing procedure to wait until some other procedure executes the appropriate event-triggering statement (for example, -> trig).

4). Level-sensitive event control:

The execution of a procedural statement can also be delayed until a condition becomes true. This is

accomplished using the wait statement, which is a special form of event control. The nature of the wait

statement is level-sensitive, as opposed to basic event control (specified by the @ character), which is edge sensitive.

The wait statement shall evaluate a condition; and, if it is false, the procedural statements following the wait statement shall remain blocked until that condition becomes true before continuing.

The following example shows the use of the wait statement to accomplish level-sensitive event control:

begin

wait (!enable) #10 a = b;

#10 c = d;

end

If the value of enable is 1 when the block is entered, the wait statement will delay the evaluation of the next statement (#10 a = b;) until the value of enable changes to 0. If enable is already 0 when the begin end block is entered, then the assignment “a = b;” is evaluated after a delay of 10 and no additional delay

occurs.

<< Previous | Next >>