This describes system tasks and functions that are considered part of the Verilog-AMS HDL. It

also states whether a particular system task or function is supported in the digital context and if it is supported in the analog context. The system tasks and functions are divided into various categories.

1). Display system tasks:

The display group of system tasks is divided into three categories: the display and write tasks, strobed

monitoring tasks, and continuous monitoring tasks.

$strobe ( list_of_arguments ) ; — It provides the ability to display simulation data when the simulator has converged on a solution for all nodes.

$display ( list_of_arguments ) ; — It provides the same capabilities as $strobe

$monitor ( list_of_arguments ) ; — It provides the ability to monitor and display the values of any variables or expressions specified as arguments to the task.

$debug( list_of_arguments ) ; — It provides the capability to display simulation data while the analog simulator is solving the equations; it displays its arguments for each iteration of the analog solver.

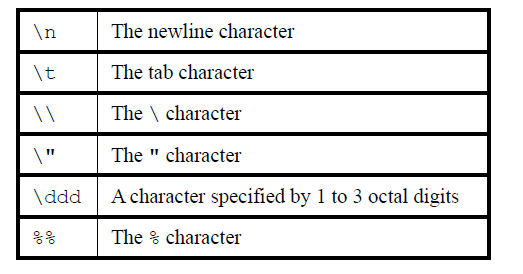

Escape sequences for printing special characters: The escape sequences shown in below Table, when included in a string argument, print special characters.

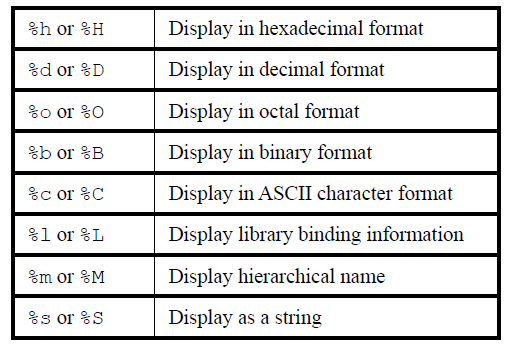

Escape sequences for format specifications: The special character % indicates that the next character should be interpreted as a format specification that establishes the display format for a subsequent expression argument.

2) File input-output system tasks and functions:

The system tasks and functions for file-based operations are divided into the following categories:

— Functions and tasks that open and close files

— Tasks that output values into files

— Tasks that output values into variables

— Tasks and functions that read values from files and load into variables or memories

Opening and closing files: $fopen and $fclose–

fd = $fopen ( ” file_name ” , type ) ;

$fclose ( fd ) ;

The function $fopen opens the file specified as the filename argument and returns either a 32-bit

multichannel descriptor or a 32-bit file descriptor determined by the absence or presence of the type

argument.

filename is a character string or is a reg containing a character string that names the file to be opened.

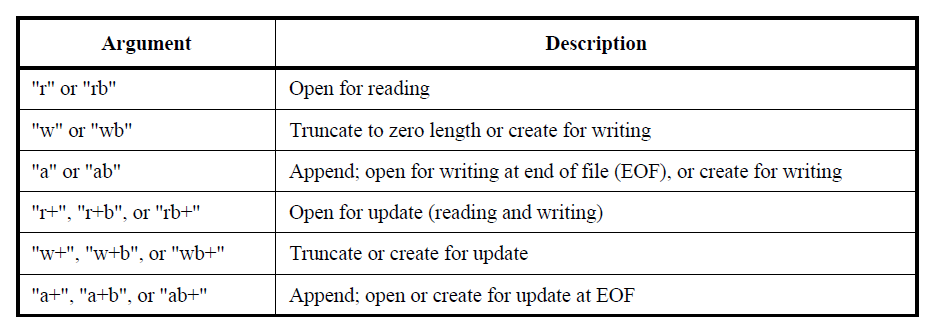

Types for file descriptors–

3) Simulation control system tasks:

There are two simulation control system tasks:

a) $finish [ ( n ) ]

b) $stop [ ( n ) ]

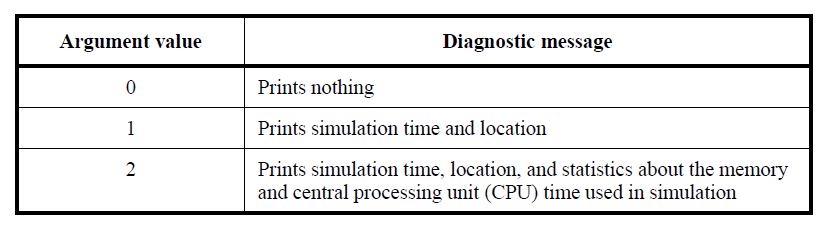

The $finish system task simply makes the simulator exit and pass control back to the host operating system. If an expression is supplied to this task, then its value (0, 1, or 2) determines the diagnostic messages that are printed before the prompt is issued as shown in below Table. If no argument is supplied, then a value of 1 is taken as the default.

The $stop system task causes simulation to be suspended. This task takes an optional expression argument (0, 1, or 2) that determines what type of diagnostic message is printed. The amount of diagnostic messages output increases with the value of the optional argument passed to $stop.

<< Previous | Next >>